It’s no secret Intel is readying the next generation of Xeon datacentre and workstation processors for release in Q1 this year. Known by the codename ‘Sapphire Rapids’ and using the latest Golden Cove architecture, 4th Gen Xeons leverage a tiled/chiplet approach for expanding core counts, caches and performance, particularly for AI tasks.

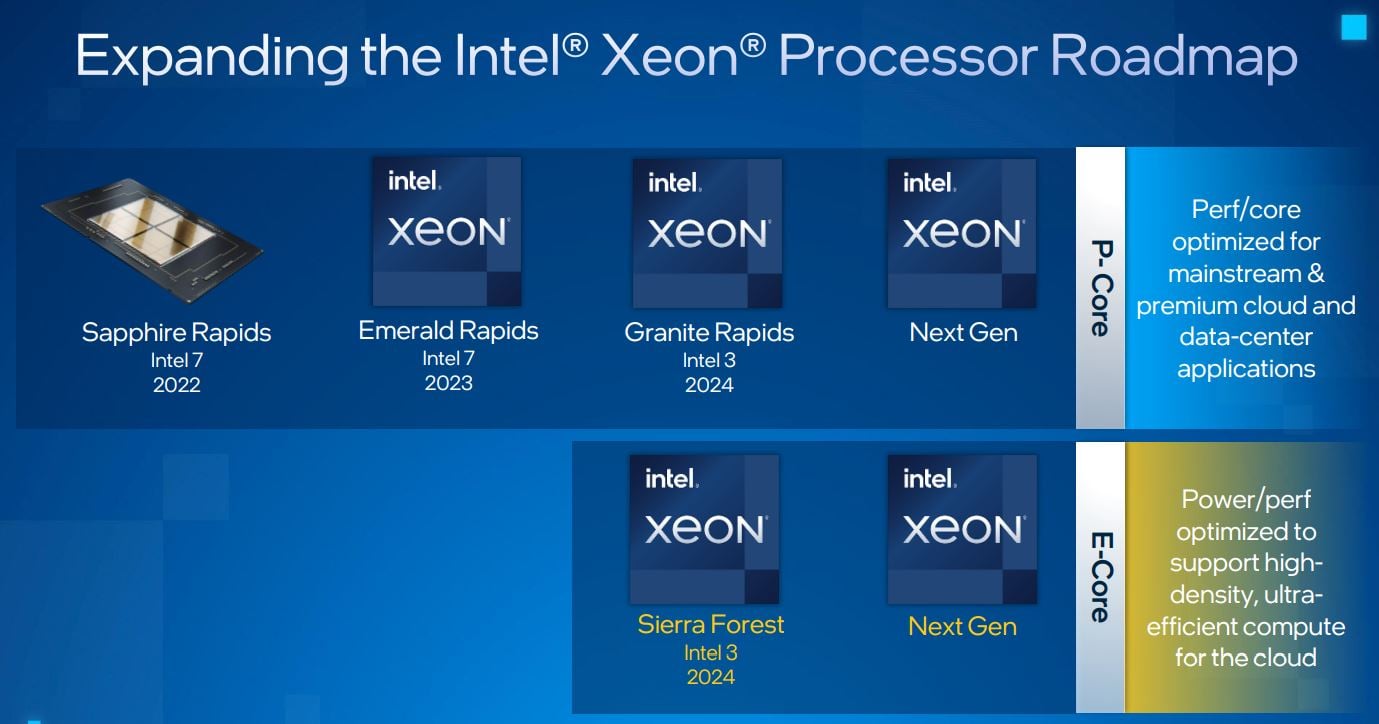

Looking further out, Intel provided more details on the Xeon roadmap during an Investor Day meeting this afternoon. Key announcements include an acceleration of next-generation process technology and introduction of E-core-only Xeons in 2024.

With respect to high-performance computing, Intel officially announces ‘Emerald Rapids’ as the successor to Sapphire Rapids. It’s coming next year and is considered a general refresh. Built on Intel 7 process whilst harnessing the existing platform, Emerald Rapids is set to use enhanced Raptor Cove Performance compute cores and focus on expanding memory capabilities and security.

Moving further out, into 2024, Intel will debut ‘Granite Rapids’ P-core-only Xeons. These have been referenced publicly in previous updates but, in a call with Ronak Singhal, senior Intel fellow, Club386 learned the manufacturing process is being upgraded from Intel 4 to Intel 3, alongside the introduction of a brand-new platform. Even further out, there’s likely a Granite Rapids refresh currently known as ‘Diamond Rapids,’ though the naming convention is conjecture on our part. To be clear, each iterative Xeon in this line-up uses P cores alone and is primed for high-performance compute and heavy-duty AI processing.

E-core Xeons coming soon

Arguably bigger news is the announcement of a separate line of Xeon processors built solely with energy-efficient E cores. Optimised for density and performance per watt, Intel spies a lucrative opportunity for customers whose specific workloads respond better to processors with greater thread parallelism within a given power and silicon envelope.

Rather than having P cores scale down the frequency and voltage ladder to accommodate this growing area, Intel says it has responded to large-scale customers’ demands for Xeons with different performance characteristics. It’s likely that cloud and hyperscale providers will adopt a mixture of P- and E-core Xeons in their arsenal, depending upon exact workload. That said, there will be no Xeons using a hybrid architecture in one package, unlike desktop-optimised Alder Lake.

The first Xeon E-core chips debut in 2024 under the ‘Sierra Forest’ codename. Using the same platform as Granite Rapids, and also built on Intel 3 process, they feature identical memory controllers, PCIe support and so forth. Sierra Forest’s use of E cores fundamentally changes the size and efficiency of execution engines and caching structures, so exactly how this platform-level compatibility works in practise is yet to be finalised, though Lisa Spelman, corporate vice president and general manager of the Xeon and Memory Group, shed further light.

“Although we are introducing a new core architecture into our Xeon Platform product line, we were intentional about ensuring it remained compatible with the vast Xeon platform ecosystem that exists today. But these next-generation processors will share more than just platform, software and BIOS. Within the CPU package, we will decouple core and uncore functions into “compute tiles” and “I/O tiles,” with the I/O tiles being common between P-core and E-core based products, enabling a common I/O subsystem to be used.”

It is possible E-core-only SKUs will perform better than P-core Xeons at the same power budget, and vice versa, meaning adoption will be undertaken on a workload-by-workload basis. As Intel is selling large-volume Xeons into providers who understand throughput and requirements intimately, exact rack configuration ought to be relatively straightforward.

Quite how these E-core-only models are branded remains a mystery, too, as Intel has a number of ‘Xeon E’ chips in the present line-up.

A two-pronged Xeon compute-core strategy is here to stay. Whether this announcement ultimately ends up as a tacit admission that a single Intel architecture cannot scale to serve all markets, or is viewed in hindsight as a wise move in extracting more potential TAM that’s currently being exploited by rivals by Arm and AMD, remains to be seen.