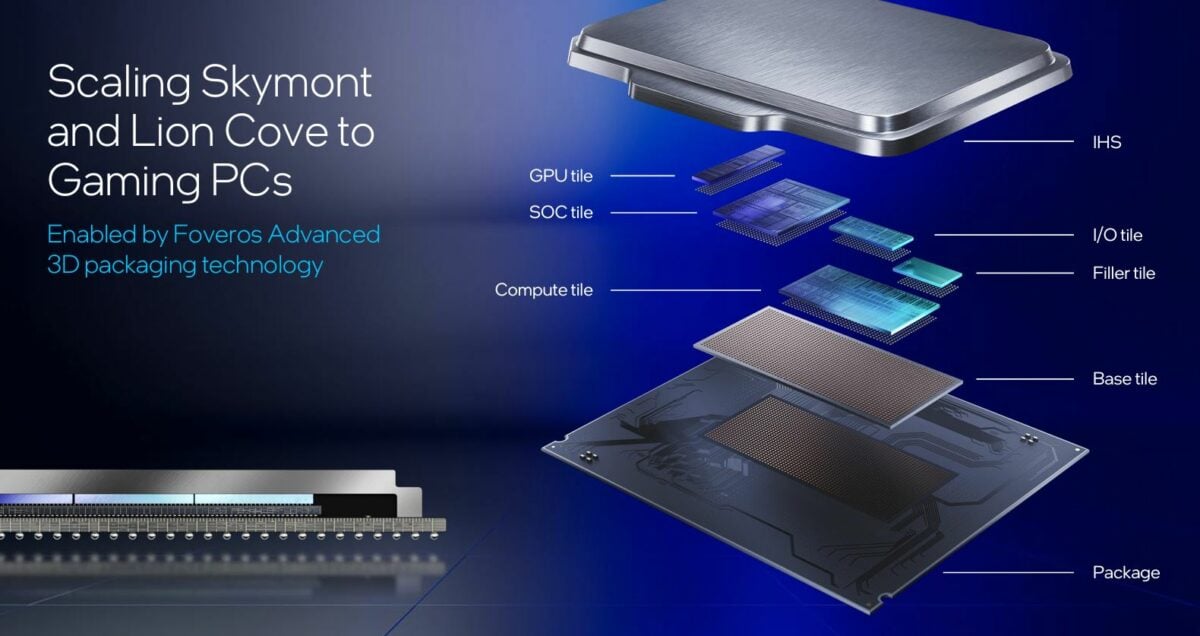

Intel is seemingly considering a major change to its tile-based design, starting with the Panther Lake architecture. The brand is expected to integrate the memory controller back inside the compute die.

According to @kopite7kimi on X, Intel is reintegrating the IMC (Integrated Memory Controller) into the compute die. One of the reasons behind this move seems to be the higher latency stemming from separating the controller inside a different tile, away from the CPU cores. Another could be combatting limitations, such as the absence of Hyperthreading and lower frequencies, which hinder current-gen Arrow Lake chips.

That said, performance may not be the only reason pushing Intel to move its IMC back inside the compute die/tile. According to @jaykihn0, all subsystems that are generally located in the SOC – like the NPU – will be relocated to the compute tile since Panther Lake lacks a dedicated SOC tile. The latter’s absence is apparently due to scaling. Moreover, the leaker had indicated that this change will only be applied to this generation, meaning that the following generations should go back to the same SOC/Compute design found on Meteor Lake and Arrow Lake.

To put it simply, Meteor Lake had its IMC inside the SOC tile. Panther Lake will reportedly bring it to the Compute tile, while Nova Lake should relocate it back to the SOC tile. Intel is playing ping-pong. The brand seems to be experimenting in search of the best compromise between production cost and performance.

As a reminder, not all tiles are manufactured using the same node. For example, Arrow Lake’s Compute tile is built using TSMC’s N3B node, contrary to the I/O tile, which leverages the older and cheaper N6 process. Choosing old nodes for secondary tiles also means less demand for leading-edge manufacturing, freeing up capacity for parts that benefit from new processes. Not to mention that making multiple small dies instead of a single large one reduces the effects of defects, as bad sections would take less wafer space.

Regardless of the reason, if Intel is truly relocating its IMC inside the Compute tile, then latency and performance could benefit greatly from a shorter distance to the CPU cores.